# Evaluating the Top Electrode Material for Achieving an Equivalent Oxide Thickness Smaller than 0.4 nm from an Al-Doped TiO<sub>2</sub> Film

Woojin Jeon,<sup>†</sup> Sijung Yoo,<sup>†</sup> Hyo Kyeom Kim,<sup>†</sup> Woongkyu Lee,<sup>†</sup> Cheol Hyun An,<sup>†</sup> Min Jung Chung,<sup>†</sup> Cheol Jin Cho,<sup>†,‡</sup> Seong Keun Kim,<sup>‡</sup> and Cheol Seong Hwang<sup>\*,†</sup>

<sup>†</sup>Department of Materials Science and Engineering and Inter-university Semiconductor Research Center, Seoul National University, 1 Gwanak-ro, Gwanak-gu, Seoul 151-742, Republic of Korea

<sup>‡</sup>Electronic Materials Research Center, Korea Institute of Science and Technology, Seoul 136-791, Republic of Korea

**ABSTRACT:** The effects of Pt and RuO<sub>2</sub> top electrodes on the electrical properties of capacitors with Al-doped TiO<sub>2</sub> (ATO) films grown on the RuO<sub>2</sub> bottom electrode by an atomic layer deposition method were examined. The rutile phase ATO films with high bulk dielectric constant (>80) were well-grown because of the local epitaxial relationship with the rutile structured RuO<sub>2</sub> bottom electrode. However, the interface between top electrode and ATO was damaged during the sputtering process of the top electrode, resulting in the decrease in the dielectric constant. Postmetallization annealing at 400 °C was performed to mitigate the sputtering

damage. During the postmetallization annealing, the ATO layer near the RuO<sub>2</sub> top electrode/ATO interface was well-crystallized because of the structural compatibility between RuO<sub>2</sub> and rutile ATO, while the ATO layer near the Pt top electrode/ATO interface still exhibited an amorphous-like structure. Despite the same thickness of the ATO films, therefore, the capacitors with RuO<sub>2</sub> top electrodes showed higher capacitance compared to the capacitors with Pt top electrodes. Eventually, an extremely low equivalent oxide thickness of 0.37 nm with low enough leakage current density ( $<1 \times 10^{-7}$  A/cm<sup>2</sup> at 0.8 V) and physical thickness of 8.7 nm for the next-generation dynamic random access memory was achieved from ATO films with RuO<sub>2</sub> top electrodes.

KEYWORDS: atomic layer deposition, Al-doped TiO<sub>2</sub>, dead-layer effect, equivalent oxide thickness, RuO<sub>2</sub>, Pt, postmetallization anneal

## INTRODUCTION

Many high-dielectric-constant ( $\kappa$ ) materials have been examined for capacitor application in the next-generation dynamic random access memory (DRAM).<sup>1-3</sup> The most important requirements for a capacitor dielectric have been a high  $\kappa$  value for higher capacitance and a lower leakage current density (I)that will allow the charge to be stored for a sufficiently long time. It has been well-known that the dielectric constant and the leakage current have a trade-off relationship for almost all the high- $\kappa$  dielectric materials.<sup>4</sup> The presently adopted capacitor dielectric layer in the mass production DRAM is the ZrO<sub>2</sub>/ Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub> (ZAZ) stack, where a ZrO<sub>2</sub> layer with a  $\kappa$  value of 30-40 provides the capacitor with a high capacitance density whereas the thin ( $\sim 1$  nm) Al<sub>2</sub>O<sub>3</sub> interlayer plays the role of a leakage current suppressor.<sup>5,6</sup> The high  $\kappa$  value of ZrO<sub>2</sub> is most fluently achieved on a TiN electrode, whose fabrication process technology into the extremely small storage node geometry is highly matured. This dielectric/electrode system appears capable of offering a minimum equivalent oxide thickness (EOT) down to ~0.6 nm. An even smaller EOT value (<0.5 nm), however, will soon be necessary for a further-scaled DRAM (with design rule <20 nm).<sup>7</sup> In this regard, another high- $\kappa$  material, TiO<sub>2</sub>, was extensively studied in the past decade as it is the most promising capacitor dielectric material

because of its higher  $\kappa$  value of ~100 when it has a rutile crystal structure on a Ru or  $RuO_2$  bottom electrode (BE).<sup>8-17</sup> The smaller band gap ( $\sim$ 3.1 eV) of TiO<sub>2</sub>, however, which induced a conduction band offset of  $\leq 1$  eV with noble metal electrodes (Pt, Ru, and  $RuO_2$ ), led to a severe leakage current problem. To solve this problem, Al-doping in  $TiO_2$  (Al-doped  $TiO_2$ ) ATO) was reported to be the most effective method of reducing the leakage current of TiO<sub>2</sub>, although the  $\kappa$  value of ATO is slightly lower than that of nondoped TiO<sub>2</sub>.<sup>18</sup> With this composition modification, the minimum EOT with an acceptable leakage current density ( $<1 \times 10^{-7} \text{ A/cm}^2$  at 0.8 V) was decreased to 0.48 nm on Ru BE and 0.45 nm on RuO<sub>2</sub> BE.<sup>19</sup> In both cases, the top electrode (TE) material was Pt, which has been usually regarded as the most inert metal electrode and thus the one that will not introduce any adverse interfacial low- $\kappa$  layer. Kim et al. recently reported, however, that this is not necessarily the case when the high- $\kappa$  HfO<sub>2</sub> dielectric film on a Si substrate becomes very thin, which was ascribed to the damaging effect of Pt deposition even though the Pt deposition process was optimized in the study to induce

Received: September 29, 2014 Accepted: November 17, 2014 Published: November 17, 2014

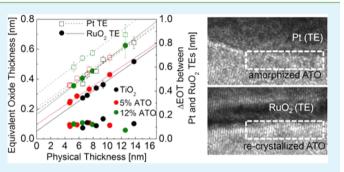

**Figure 1.** (a) Difference in C-V curve of the 9.5 nm thick ATO film (5% Al) deposited on RuO<sub>2</sub> with respect to RuO<sub>2</sub> (red) and Pt (black) TE, and before (open) and after (closed) the PMA process. (b) EOT (left axis) vs POT of the TiO<sub>2</sub> and ATO films for RuO<sub>2</sub> (closed) and Pt (open) TE, and EOT difference (right axis) between Pt and RuO<sub>2</sub> TE for each TiO<sub>2</sub> and ATO film.

a significant physical and chemical damaging effect.<sup>20,21</sup> Kim et al. found that replacing the Pt gate electrode with RuO<sub>2</sub> could decrease the EOT by ~0.4–0.5 nm for the given HfO<sub>2</sub> thickness. This was an unexpected result because according to the recent theoretical results on the interfacial dead-layer effect of the ferroelectric thin films depending on the electrode type (e.g., Pt, Au, and SrRuO<sub>3</sub>), Pt is supposed to induce the least dead-layer effect thanks to its much higher carrier concentration compared with oxide electrodes.<sup>22,23</sup> This implies that there could be an extrinsic effect, which was not taken into account during the theoretical calculation.

It is highly probable that the highly energetic bombardment effect of heavy metal atoms, such as Pt or Ru, on the dielectric layer to form the TE could induce an unavoidable damaging effect at least to the top portion of the thin dielectric films. This must be the case even with a careful tuning of the TE deposition conditions, as long as the energetic particles are used, such as sputtering or electron beam evaporation. In fact, it was observed that 2-3 nm of a  $\sim 10$  nm thick HfO<sub>2</sub> gate dielectric film was even etched away during the sputter deposition of the Pt gate electrode, especially when the oblique-angle incidence sputter geometry was adopted (unpublished data from the authors' group).

Therefore, in this work, such interfacial damaging layer effect, which could be imposed during the TE deposition on the ATO thin films for fabricating the metal-insulator-metal (MIM) capacitor structure, was focused on, and a method of alleviating or curing such damage effect was studied. It was found that adopting RuO<sub>2</sub> TE was highly effective for curing such damaging layer during the postmetallization annealing step (PMA) after the TE deposition due possibly to the local epitaxial correlation between the ATO layer and RuO<sub>2</sub> TE. While the ATO MIM capacitor with the Pt TE already showed a highly promising performance in terms of scaling down the EOT to 0.45 nm, this further decreased the EOT by almost 0.1 nm over a large thickness range. As a result of such improvement, a minimum EOT of 0.37 nm with an acceptable leakage current density  $(4 \times 10^{-8} \text{ and } 2 \times 10^{-7} \text{ A/cm}^2 \text{ at } 0.8$ and 1.0 V, respectively) and adequate physical thickness of 8.7 nm for the next-generation DRAM capacitor was achieved, which is the smallest EOT reported in this field to the authors' knowledge.

#### EXPERIMENTAL SECTION

$TiO_2$  and ATO films were deposited using a traveling-wave-type atomic layer deposition (ALD) reactor on  $RuO_2(40 \text{ nm})/SiO_2(100 \text{ nm})/Si$  substrates at a wafer temperature of 250 °C.  $Ti(OC_3H_7)_4$  and  $Al(CH_3)_3$  were used as the Ti and Al precursors, respectively, and  $O_3$  with a concentration of 250 g/m<sup>3</sup> was used as the oxygen source. To

incorporate Al atoms into the films, Al-O deposition cycles were introduced discretely into the TiO2 film, but the Al atoms diffused quite uniformly across the entire film thickness. The concentration of Al in the bulk film was controlled by varying the Al-O and Ti-O deposition cycle ratio, and 5 and 12 atomic % ([Al]/[Ti + Al]) Al concentrations were achieved when the Al-O:Ti-O deposition cycle ratio was 1:100 and 3:100, respectively. The details for the ALD processes were reported elsewhere.<sup>18</sup> These process conditions and the adoption of a rutile-structured RuO2 BE resulted in rutilestructured TiO<sub>2</sub> and ATO films. For controlling the crystal structure to anatase phase for comparison, Pt was also adopted as the BE in several cases, but in general, RuO<sub>2</sub> was the BE material otherwise stated. For the electrical property measurements, 80 nm thick Pt and 30 nm thick RuO<sub>2</sub> TE, respectively, were fabricated via DC and RF sputtering using a shadow mask with a 300  $\mu$ m diameter. On the RuO<sub>2</sub> layer, additional 50 nm-thick Pt was deposited to improve the contact during probing. The detailed sputtering process conditions for the least damaging effect to the high- $\kappa$  dielectric films were reported elsewhere,<sup>20</sup> but a minimum level of damage was still unavoidable. After depositing the TEs, PMA was performed at 400 °C for 30 min under a N<sub>2</sub> 95%/O<sub>2</sub> 5% atmosphere in a tube furnace. The film thickness was determined through calculation from the layer density, which was measured via Xray fluorescence (XRF, Thermo Scientific, ARL Quant'X), and the film density via X-ray reflection (XRR, PANalytical, X'Pert Pro). XRR and spectroscopic ellipsometry (Woollam, ESM-300) was used to estimate the film thickness too for several cases. XRF cannot detect oxygen so that the estimated layer density of Ti was used to check the amount of the deposited TiO<sub>2</sub> film. The microstructures of the films were analyzed using a high-resolution transmission electron microscope (HRTEM, Tecnai F20, field emission, 200 kV). The electrical properties were measured through capacitance-voltage (C-V) and current density-voltage (J-V) measurement using HP 4140D and 4194A, respectively, at room temperature.

#### RESULTS AND DISCUSSION

Figure 1a shows the C-V curves of the 9.5 nm thick ATO films (5% Al) with Pt and RuO<sub>2</sub> TE before and after the PMA, respectively. BE was commonly RuO2. Even though all the other parameters were identical, except for the materials for the TE, a large difference in capacitance density was found in both capacitors. For the RuO2TE, high capacitance density of approximately 90 fF/ $\mu$ m<sup>2</sup> was obtained at 0 V whereas the capacitance of the ATO film with the Pt TE was only 65 fF/  $\mu m^2$  even after the PMA. From the comparison between the cases before and after the PMA, it was found that a large increase in capacitance density for the case of RuO2 TE was achieved during the PMA. Due to the very large leakage current under the negative bias condition, the capacitance of the sample with Pt TE before PMA cannot be accurately estimated in that voltage region. To understand the reasons for such improvement, the variation in the EOT with respect to the film thickness was examined. Figure 1b shows the variation in the

**Research Article**

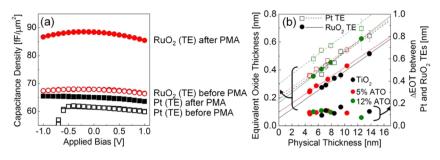

**Figure 2.** (a) *J*-EOT and (b) *J*-POT curve of the 5% ATO films with Pt (black) and RuO<sub>2</sub> (red) TE, respectively. In *J*-EOT curve (a), the *J* values measured at +0.8 and -0.8 V are indicated as closed and open symbols, respectively. (c) *J*–*V* curve of the MIM capacitor, which consisted of RuO<sub>2</sub>/ 5%, 8.7 nm ATO/RuO<sub>2</sub> with 0.37 nm EOT.

EOT of the TiO2 and ATO films with 5 and 12% Al concentrations (5 and 12% ATO) with the Pt and RuO<sub>2</sub> TE, respectively, as a function of their physical oxide thickness (POT) after the PMA. The bulk dielectric constants of  $TiO_{2}$ , 5% ATO, and 12% ATO, which were calculated from the inverse slope of the linear fit graphs, were 106.7, 99.7, and 86.3, respectively. The slopes of the linear fit graphs of the materials were almost identical irrespective of the TE material. This means that the large difference in capacitance density in Figure 1a was not induced by the change in the bulk properties, including the possible outward diffusion of Al into the RuO2 electrode.<sup>13</sup> Interestingly, a certain difference (approximately 0.1 nm) in the y-intercept between the Pt and  $RuO_2$  TEs was observed for all the three cases: the capacitors with Pt TE showed a higher EOT than those with RuO<sub>2</sub> TE. This means that the interfacial layer between Pt TE and TiO<sub>2</sub> or ATO has a lower dielectric constant than the interfacial layer between  $RuO_2$  TE and  $TiO_2$  or ATO, which is the main reason for the higher capacitance density of ATO with RuO<sub>2</sub> TE in Figure 1a.

While the work function can hardly be the only parameter that determines the electron injection at the cathode interface, due to the possible involvement of Fermi level pinning and several other effects, a higher-work-function metal generally tends to induce a lower leakage current.<sup>19</sup> Hence, it can be said that the leakage current due to the slightly smaller work function (~5.1 eV) of RuO<sub>2</sub> compared with Pt (~5.6 eV) may induce a leakage current problem for RuO<sub>2</sub> TE. Nevertheless, the EOT decrease effect from the adoption of RuO<sub>2</sub> overcompensates for such loss in J and largely improves the J-EOT performance, which is the most critical parameter for the MIM capacitor for DRAM, as shown in Figure 2a.

Figure 2a, b show the plot of J measured at +0.8 and -0.8 V versus the EOT and the POT of the ATO layers with a 5% Al concentration with Pt or RuO<sub>2</sub> TE, respectively. The data for the higher-Al-concentration (12%) ATO were not included in the figure because the electrical properties of the 12% ATO films were generally inferior to those of the 5% ATO films. The EOT of the samples with RuO<sub>2</sub> TE was approximately 0.05-0.1 nm lower than that of the samples with Pt TE at an identical J level in the whole range. The lowest EOT value of 0.37 nm with a J value of  $4.0 \times 10^{-8}$  A/cm<sup>2</sup> at +0.8 V, 2.3 ×  $10^{-7}$  A/cm<sup>2</sup> at +1.0 V, and 2.8 ×  $10^{-8}$  A/cm<sup>2</sup> at -0.8 V was achieved from the symmetric MIM capacitor (RuO2/5%, 8.7 nm-thick ATO/RuO<sub>2</sub>) with adequate physical thickness of 8.7 nm, which is the best electrical performance reported from the ALD high- $\kappa$  capacitor dielectric in this field. Such high performance is comparable to that of the even-higher- $\kappa$  dielectric film of SrTiO<sub>3</sub>.<sup>24-28</sup> Figure 2c shows the J-V curves of this highest-performance sample in the positive and negative bias regions.

It was expected from the first-principles calculation that Pt would show a lower interfacial dead-layer effect compared to RuO<sub>2</sub> when the electrode was contact with a dielectric layer.<sup>22</sup> The inverse trend in this work compared with the theoretical expectation may have been induced by the extrinsic effects, such as the presence of interfacial low- $\kappa$  layers due probably to the physical damaging effect from the TE deposition. To clarify the microstructure change at the interface by TE sputtering, the interface between TE and ATO was observed via cross-section HRTEM. Figure 3a, b shows the cross-section HRTEM images

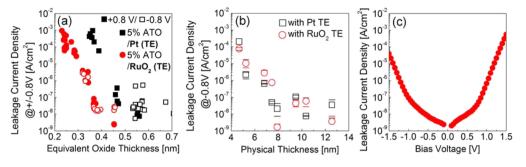

**Figure 3.** Cross-sectional TEM images of the (a, c, e)  $(BE)RuO_2/10$  nm thick ATO/Pt(TE) and (b, d, e)  $(BE)RuO_2/10$  nm thick ATO/RuO<sub>2</sub>(TE). (c, d) and (e, f) Images for the interface between ATO and TE and between ATO and BE, respectively, indicated as red boxes in (a) and (b).

of the 5% ATO film (nominal thickness: 10 nm) with Pt and  $RuO_2$  TE, respectively, where the BE was  $RuO_2$ . Due to the polycrystalline nature of the whole stacked films, many HRTEM images were taken, and the most representative images were selected to show the critical difference between the interfaces with Pt and  $RuO_2$  TE. Figure 3c, e shows enlarged images of the portions indicated by the red boxes in Figure 3a,

## **ACS Applied Materials & Interfaces**

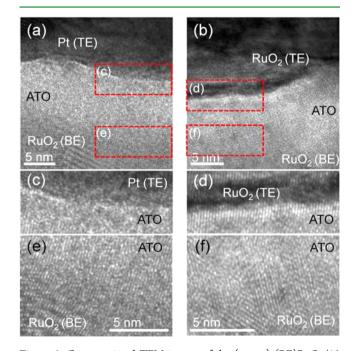

which clearly show the features of the interface region of the ATO film near the TE and BE, respectively. Figure 3d, f shows the same for the RuO<sub>2</sub> TE. It is well-known that RuO<sub>2</sub> and rutile TiO<sub>2</sub> have identical rutile crystal structures with a very small lattice mismatch (2.09 and -4.76% on the *a*- and *c*-axes, respectively), which derived the local epitaxial growth of the rutile TiO<sub>2</sub> film on the RuO<sub>2</sub> film.<sup>10</sup> This was the main reason that the higher- $\kappa$  rutile TiO<sub>2</sub> could be formed under the conditions where anatase TiO<sub>2</sub>, whose  $\kappa$  value is ~40, is stable.<sup>10</sup> The local epitaxial growth was indeed confirmed from the HRTEM images of the ATO/RuO<sub>2</sub> BE interface in Figure 3e, f, showing the continuous lattice fringes across the RuO<sub>2</sub> BE and ATO dielectric regions. This was also the case in Figure 3d, where continuous lattice fringes are observed across the ATO and RuO<sub>2</sub> TE regions. In contrast, this was certainly not the case at the ATO/Pt TE interface (Figure 3c). This coincidence of crystal structure between top electrode and ATO film was more clearly observed in Fast Fourier Transform (FFT) images (Figure 4). Although the bulk regions of ATO and Pt TE were

Figure 4. FFT patterns from (a, c, e) 10 nm thick ATO/Pt(TE) (Figure 3c) and (b, d, e) 10 nm thick  $ATO/RuO_2(TE)$  (Figure 3d), respectively. (a, b) and (c, d) Images for each TE and the interface between ATO and TE. (e, f) images of ATO film.

crystallized, the interface remained amorphous. This is believed to be the origin of the higher *y*-axis intercept of the EOT-POT plots in Figure 1b, and if the  $\kappa$  values of these amorphized layer of Pt TE and recrystallized layer of RuO<sub>2</sub> TE are assumed to be ~20 and 40, respectively, which must be reasonable, this ~1 nm thick sputtering-damaged region must induce a ~0.1 nm EOT difference.

This difference can be ascribed to the TE-dependent recrystallization effect of the damaged region near the TE during the PMA. The sputter deposition of Pt TE on the ATO could induce the physical damage to the top portion of the ATO film due to the energetic impingement effect of the heavy Pt atoms. This can be evidently confirmed from the amorphous-like ATO region near the TE even after the PMA. The disparate crystal structures of rutile  $TiO_2$  (ATO) and cubic (FCC) Pt cannot induce the TE-induced recrystallization of the amorphous-like ATO region during PMA. In contrast, the similar crystal structure of RuO<sub>2</sub> TE and ATO can fluently induce the recrystallization of the possible damaged layer of ATO near the RuO2 TE. It had not been structurally confirmed that the ATO region near the RuO<sub>2</sub> TE before the PMA actually had a damaged structure, but the capacitance density of the RuO<sub>2</sub>/ATO/RuO<sub>2</sub> samples before PMA was significantly lower than that after PMA (Figure 1a), which is even comparable to that of Pt TE, suggesting that there was certainly a damaged layer or that the crystalline quality of the overall dielectric film was not as good as that after PMA. On the other hand, the J under negative bias application, which represents the properties of the TE interface, was certainly higher than that under the positive bias application, which represents the properties of the BE interface, before PMA (data not shown), whereas the two values became almost identical after PMA, as can be seen from Figure 2c. This indicates that the ATO near the RuO<sub>2</sub> TE interface was also damaged by the sputter impingement effect.

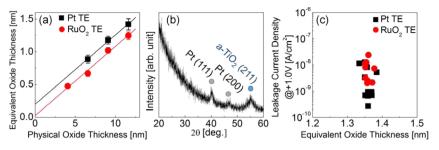

To further confirm the hypothesis for the improvement by adopting RuO<sub>2</sub> TE, two more sets of experiments were performed, as shown in Figure 5. The first set of experiments was performed with ATO (5% Al) films, with Pt or RuO<sub>2</sub> TE, but the critical difference was that the films were grown on a Pt electrode, which resulted in an anatase-structured ATO film, as confirmed via glancing-angle incidence X-ray diffraction (GIXRD, denoted as a-TiO<sub>2</sub> in Figure 5b). The values of the bulk dielectric constant of the anatase ATO film with RuO2 and Pt TE calculated from the slope of the EOT-POT curve (Figure 5a) were almost identically small (36.8) when calculated from the inverse of the slope of the best-linear-fitted graphs. The difference in the y-intercepts of the two fitting graphs was  $\sim 0.17$  nm. Although this is slightly higher than the difference for the rutile ATO films with Pt and RuO<sub>2</sub> TE, the certainly higher *y*-intercept from the Pt TE samples clearly indicates that the aforementioned damage recovery mechanism can work even for the anatase film. It is believed that the amorphized ATO region near RuO<sub>2</sub> TE, which was supposed to be crystalline anatase before TE deposition, was recrystallized to rutile TiO<sub>2</sub>, whereas the same damage region below Pt TE could not undergo the same transition.

Another supporting proof can be found in Figure 5c, which shows the summary of the *J* vs EOT plots of the ~10 nm thick ZAZ films grown on TiN BE, with Pt and RuO<sub>2</sub> TE. The ZAZ dielectric films were supplied by a DRAM chip manufacturer. In this case, there was no clear tendency in the EOT values between the two groups. This can be ascribed to the unoptimized PMA condition for the ZAZ dielectric layer. It is most likely due to the fact, however, that the ZAZ layer, especially the top  $ZrO_2$  layer, which is in contact with TE, had no common crystallographic feature with both TE materials.  $ZrO_2$  should be either monoclinic or tetragonal under the process conditions, and as such, it could not have a local epitaxial relation with Pt. The lattice parameters of tetragonal

**Research Article**

Figure 5. (a) EOT-POT plots of (BE)Pt/anatase ATO/Pt(TE) (black) and (BE)Pt/anatase ATO/RuO<sub>2</sub>(TE) (red). (b) GIXRD pattern of ATO film on Pt electrode. a-TiO<sub>2</sub> means anatase TiO<sub>2</sub> (c) *J*-EOT plots of (BE)TiN/5 nm-thick ZAZ/Pt(TE) (black) and (BE)TiN/5 nm-thick ZAZ/RuO<sub>2</sub>(TE) (red).

$ZrO_2$  are quite different from those of tetragonal (rutile)  $RuO_2$ , and the ionic arrangements in the cubic fluorite-derived  $ZrO_2$ structure shares no common feature with those of the rutile  $RuO_2$  structure. Therefore, even  $RuO_2$  TE has little possibility of recovering the possible damaged layer.

## CONCLUSION

In summary, significant EOT scaling by ~0.1 nm (from 0.45-0.48 to 0.37 nm) was achieved from an 8.7 nm-thick ALD ATO (5% Al concentration) film by simply changing the top electrode material from Pt to RuO<sub>2</sub>. Although Pt is regarded as the electrode material that is least likely to induce any chemically reacted or intrinsic low- $\kappa$  interface layer, this was not necessarily the case in the ATO dielectric layer due to the structural damaging effect during its growth on top of the dielectric layer. Such damaged layer appeared to have had a lower  $\kappa$  value compared with the bulk dielectric layer, which was the main limiting factor to the ultimate EOT scaling, in addition to the other possible intrinsic dead-layer effects. Although Pt TE could not recover such damaged layer, RuO<sub>2</sub> TE recovered the rutile crystal structure of the region damaged by the local epitaxy during the PMA. The leakage current degradation by the slightly smaller work function of RuO2 compared to Pt was overcompensated for by the EOT scaling effect in their J-EOT performance. This finding can contribute substantially to the development of sub-20 nm design rule DRAMs.

#### AUTHOR INFORMATION

#### Corresponding Author

\*E-mail: cheolsh@snu.ac.kr.

#### Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

This work was supported by the Future Semiconductor Device Technology Development Program (10047231) funded by MOTIE (Ministry of Trade, Industry, & Energy) and KSRC (Korea Semiconductor Research Consortium).

#### REFERENCES

(1) Kim, S. K.; Lee, S. W.; Han, J. H.; Lee, B.; Han, S.; Hwang, C. S. Capacitors with an Equivalent Oxide Thickness of <0.5 nm for Nanoscale Electronic Semiconductor Memory. *Adv. Funct. Mater.* **2010**, *20*, 2989–3003.

(2) Hwang, C. S., Atomic Layer Deposition for Microelectronic Applications. In *Atomic Layer Deposition of Nanostructured Materials*; Wiley–VCH: Weinheim, Germany, 2011; pp 159–192.

(3) Hwang, C. S. Atomic Layer Deposition for Semiconductors; Springer: New York, 2014.

(4) Robertson, J. Band Offsets of Wide-band-gap Oxides and Implications for Future Electronic Devices. J. Vac. Sci. Technol., B 2000, 18, 1785–1791.

(5) Cho, H. J.; Kim, Y. D.; Park, D. S.; Lee, E.; Park, C. H.; Jang, J. S.; Lee, K. B.; Kim, H. W.; Chae, S. J.; Ki, Y. J.; Han, I. K.; Song, Y. W. New TIT Capacitor with ZrO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub> Dielectrics for 60nm and Below DRAMs. In *Proceeding of the 36th European Solid-State Device Research Conference (ESSDERC)*; Montreux, Switzerland, Sept. 19–21, 2006 ; Institute of Electrical and Electronics Engineers: Piscataway, NJ, 2006.

(6) Kil, D.-S.; Song, H.-S.; Lee, K.-J.; Hong, K.; Kim, J.-H.; Park, K.-S.; Yeom, S.-J.; Roh, J.-S.; Kwak, N.-J.; Sohn, H.-C.; Kim, J.-W.; Park, S.-W. Development of New TiN/ZrO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub>/TiN Capacitors Extendable to 45nm Generation DRAMs Replacing HfO<sub>2</sub> Based Dielectrics, *Symposium on VLSI Technology*, Honolulu, USA, June 13–15, **2006**.

(7) International Technology Roadmap for Semiconductors Home Page. http://www.itrs.net (accessed Sept. 10, 2014).

(8) Kim, S. K.; Kim, W. D.; Kim, K. M.; Hwang, C. S.; Jeong, J. High Dielectric Constant  $TiO_2$  Thin Films on a Ru Electrode Grown at 250 Degrees C by Atomic-layer deposition. *Appl. Phys. Lett.* **2004**, *85*, 4112–4114.

(9) Fröhlich, K.; Ťapajna, M.; Rosová, A.; Dobročka, E.; Hušeková, K.; Aarik, J.; Aidla, A. Growth of High-Dielectric-Constant TiO<sub>2</sub> Films in Capacitors with RuO<sub>2</sub> Electrodes. *Electrochem. Solid-State Lett.* **2008**, *11*, G19–G21.

(10) Fröhlich, K.; Aarik, J.; Ťapajna, M.; Rosová, A.; Aidla, A.; Dobročka, E.; Hušková, K. Epitaxial Growth of High- $\kappa$  TiO<sub>2</sub> Rutile Films on RuO<sub>2</sub> Electrodes. *J. Vac. Sci. Technol., B* **2009**, *27*, 266–270. (11) Hudec, B.; Husekova, K.; Tarre, A.; Han, J. H.; Han, S.; Rosova, A.; Lee, W.; Kasikov, A.; Song, S. J.; Aarik, J.; Hwang, C. S.; Frohlich, K. Electrical Properties of TiO<sub>2</sub>-Based MIM Capacitors Deposited by TiCl<sub>4</sub> and TTIP Based Atomic Layer Deposition Processes. *Microelectron. Eng.* **2011**, *88*, 1514–1516.

(12) Racko, J.; Mikolášek, M.; Harmatha, L.; Breza, J.; Hudec, B.; Fröhlich, K.; Aarik, J.; Tarre, A.; Granzner, R.; Schwierz, F. Analysis of Leakage Current Mechanisms in RuO<sub>2</sub>-TiO<sub>2</sub>-RuO<sub>2</sub> MIM Structures. *J. Vac. Sci. Technol., B* **2011**, *29*, 01AC08.

(13) Hudec, B.; Hušeková, K.; Dobročka, E.; Aarik, J.; Rammula, R.; Kasikov, A.; Tarre, A.; Vincze, A.; Fröhlich, K. Atomic Layer Deposition Grown Metal-Insulator-Metal Capacitors with  $RuO_2$ Electrodes and Al-doped Rutile  $TiO_2$  Dielectric Layer. J. Vac. Sci. Technol., B 2011, 29, 01AC09.

(14) Hudec, B.; Hušeková, K.; Rosová, A.; Šoltýs, J.; Rammula, R.; Kasikov, A.; Uustare, T.; Mičušík, M.; Omastová, M.; Aarik, J.; Fröhlich, K. Impact of Plasma Treatment on Electrical Properties of  $TiO_2/RuO_2$  Based DRAM Capacitor. *J. Phys. D: Appl. Phys.* **2013**, *46*, 385304.

(15) Murakami, K.; Rommel, M.; Hudec, B.; Rosová, A.; Hušeková,

K.; Dobročka, E.; Rammula, R.; Kasikov, A.; Han, J. H.; Lee, W.; Song,

S. J.; Paskaleva, A.; Bauer, A. J.; Frey, L.; Fröhlich, K.; Aarik, J.; Hwang,

C. S. Nanoscale Characterization of TiO<sub>2</sub> Films Grown by Atomic

#### **ACS Applied Materials & Interfaces**

(16) Aarik, J.; Arroval, T.; Aarik, L.; Rammula, R.; Kasikov, A.; Mändar, H.; Hudec, B.; Hušeková, K.; Fröhlich, K. Atomic Layer Deposition of Rutile-phase  $TiO_2$  on  $RuO_2$  from  $TiCl_4$  and  $O_3$ : Growth of High-Permittivity Dielectrics with Low Leakage Current. *J. Cryst. Growth* **2013**, 382, 61–66.

(17) Arroval, T.; Aarik, L.; Rammula, R.; Mändar, H.; Aarik, J.; Hudec, B.; Hušeková, K.; Fröhlich, K. Influence of Growth Temperature on the Structure and Electrical Properties of High-Permittivity  $TiO_2$  Films in  $TiCl_4$ -H<sub>2</sub>O and  $TiCl_4$ -O<sub>3</sub> Atomic-Layer-Deposition Processes. *Phys. Status Solidi A* **2014**, 211, 425–432.

(18) Kim, S. K.; Choi, G. J.; Lee, S. Y.; Seo, M.; Lee, S. W.; Han, J. H.; Ahn, H. S.; Han, S.; Hwang, C. S. Al-doped TiO<sub>2</sub> Films with Ultralow Leakage Currents for Next Generation DRAM Capacitors. *Adv. Mater.* **2008**, *20*, 1429.

(19) Han, J. H.; Han, S.; Lee, W.; Lee, S. W.; Kim, S. K.; Gatineau, J.; Dussarrat, C.; Hwang, C. S. Improvement in the Leakage Current Characteristic of Metal-Insulator-Metal Capacitor by Adopting RuO<sub>2</sub> Film as Bottom Electrode. *Appl. Phys. Lett.* **2011**, *99*, 022901.

(20) Kim, H. K.; Yu, I.-H.; Lee, J. H.; Park, T. J.; Seong Hwang, C. Scaling of Equivalent Oxide Thickness of Atomic Layer Deposited HfO<sub>2</sub> Film using RuO<sub>2</sub> Electrodes Suppressing the Dielectric Dead-layer Effect. *Appl. Phys. Lett.* **2012**, *101*, 172910.

(21) Kim, H. K.; Yu, I. H.; Lee, J. H.; Park, T. J.; Hwang, C. S. Controlling Work Function and Damaging Effects of Sputtered  $RuO_2$  Gate Electrodes by Changing Oxygen Gas Ratio during Sputtering. ACS Appl. Mater. Interfaces **2013**, *5*, 1327–1332.

(22) Stengel, M.; Spaldin, N. A. Origin of the Dielectric Dead Layer in Nanoscale Capacitors. *Nature* **2006**, *443*, 679–682.

(23) Hwang, C. S. Thickness-dependent Dielectric Constants of  $(Ba,Sr)TiO_3$  Thin Films with Pt or Conducting Oxide Electrodes. J. Appl. Phys. **2002**, 92, 432–437.

(24) Lee, W.; Han, J. H.; Jeon, W.; Yoo, Y. W.; Lee, S. W.; Kim, S. K.; Ko, C.-H.; Lansalot-Matras, C.; Hwang, C. S. Atomic Layer Deposition of SrTiO<sub>3</sub> Films with Cyclopentadienyl-Based Precursors for Metal– Insulator–Metal Capacitors. *Chem. Mater.* **2013**, *25*, 953–961.

(25) Swerts, J.; Popovici, M.; Kaczer, B.; Aoulaiche, M.; Redolfi, A.; Clima, S.; Caillat, C.; Wan Chih, W.; Afanasev, V. V.; Jourdan, N.; Olk, C.; Hody, H.; Van Elshocht, S.; Jurczak, M. Leakage Control in 0.4-nm EOT Ru/SrTiO<sub>x</sub>/Ru Metal-Insulator-Metal Capacitors: Process Implications. *IEEE Electron Device Lett.* **2014**, *35*, 753–755.

(26) Popovici, M.; Swerts, J.; Redolfi, A.; Kaczer, B.; Aoulaiche, M.; Radu, I.; Clima, S.; Everaert, J.-L.; Van Elshocht, S.; Jurczak, M. Low Leakage Ru-Strontium Titanate-Ru Metal-Insulator-Metal Capacitors for Sub-20 nm Technology Node in Dynamic Random Access Memory. *Appl. Phys. Lett.* **2014**, *104*, 082908.

(27) Schmelzer, S.; Bräuhaus, D.; Hoffmann-Eifert, S.; Meuffels, P.; Böttger, U.; Oberbeck, L.; Reinig, P.; Schröder, U.; Waser, R. SrTiO<sub>3</sub> Thin Film Capacitors on Silicon Substrates with Insignificant Interfacial Passive Layers. *Appl. Phys. Lett.* **2010**, *97*, 132907.

(28) Kupke, S.; Knebel, S.; Schroeder, U.; Schmelzer, S.; Bottger, U.; Mikolajick, T. Reliability of SrRuO<sub>3</sub>/SrTiO<sub>3</sub>/SrRuO<sub>3</sub> Stacks for DRAM Applications. *IEEE Electron Device Lett.* **2012**, 33, 1699–1701.